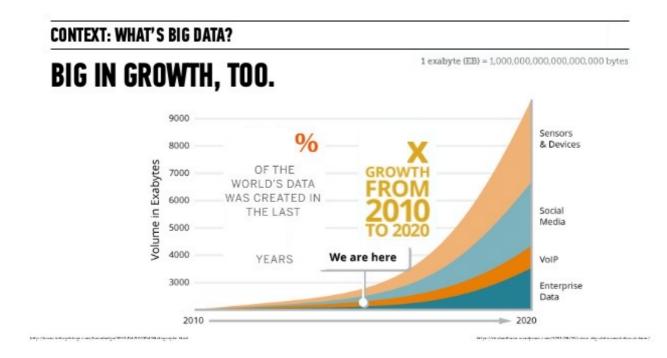

# Information Volume

Information volume has been doubled every year : \*

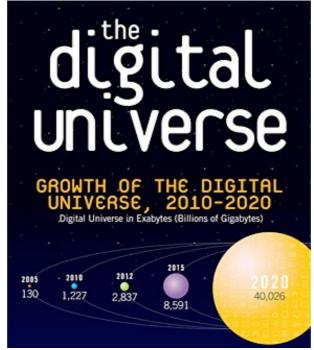

#### **Digital Universe**

Total digital information generated in the world : \*

In 2012, 2.8 ZB (=  $2.8 \times 10^{21}$  B)  $\rightarrow$  In 2020, 8.59 ZB (5.25 TB / person)

\* IDC, The Diverse and Exploding Digital Universe 2020 (11 December 2012).

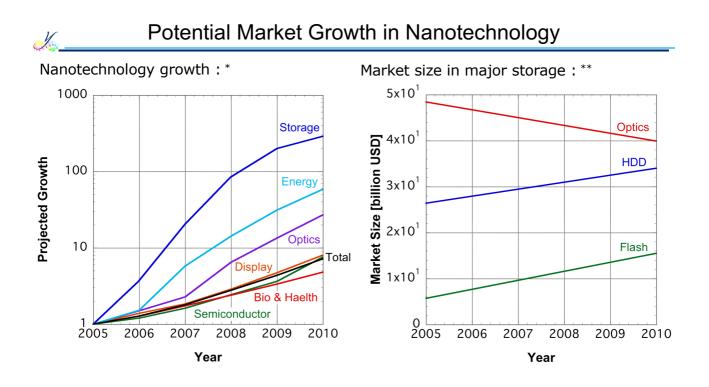

#### \* http://www.fuji-keizai.com/e/report/ww\_nano\_product\_e.html; \*\* http://www.fcr.co.jp/; http://www.yano.co.jp/

Lectures : Atsufumi Hirohata (atsufumi.hirohata@york.ac.uk, P/Z 019) Advancement in information storages and spintronics (Weeks 2 ~ 9) All lectures will be uploaded weekly in advance at <u>http://www-users.york.ac.uk/~ah566/lectures/lectures.html</u> 14:00 ~ 15:00 Mons. (SLB 101) 14:00 ~ 15:00 Thus. (SLB 101) I. Introduction to information storage (01 & 02) II. Magnetic information storages (03 ~ 06) III. Solid-state information storages (07 ~ 11) IV. Spintronic devices (12 ~ 18) Practicals : Analysis on a spintronic device using VSM, EDX, MFM and MR (Weeks 3 ~ 8)

Analysis on a spintronic device using VSM, EDX, MFM and MR (Weeks 3 ~ Operation, data and instruction will be uploaded weekly in advance at

Internal Wiki page &

http://www-users.york.ac.uk/~ah566/lectures/lectures.html

13:00 ~ 15:00 Weds. (P/A 016, Nanocentre and P/Z 008)

Continuous Assessment :

Assignment to be submitted via VLE (Week 10).

Y.

#### References

Magnetic storages :

- S. X. Wang and A. M. Taratorin, *Magnetic Information Storage Technology* (Academic Press, New York, 1999).

- C. D. Mee and E. D. Daniel, *Magnetic Recording* (McGraw Hill, New York, 1996).

Semiconductor storages :

- D. Richter, *Flash Memories: Economic Principles of Performance, Cost and Reliability Optimization* (Springer, Berlin, 2013).

- J. Brewer and M. Gill, *Nonvolatile Memory Technologies with Emphasis on Flash: A Comprehensive Guide to Understanding and Using Flash Memory Devices* (Wiley-Blackwell, New York, 2008).

Spintronics :

- A. Hirohata and K. Takanashi, *J. Phys. D: Appl. Phys.* 47, 193001 (2014).

- A. Hirohata et al., <u>J. Magn. Magn. Mater. 509</u>, 166711 (2020).

Lecture notes / slides : Internal Wiki page &

http://www-users.york.ac.uk/~ah566/lectures/lectures.html

# **01** Principles of Information Storage

Moore's law

Information storage

Von Neumann's model

Internal connections

Memory access

Bit and byte

#### Miniaturisation and Integration in Semiconductor Devices

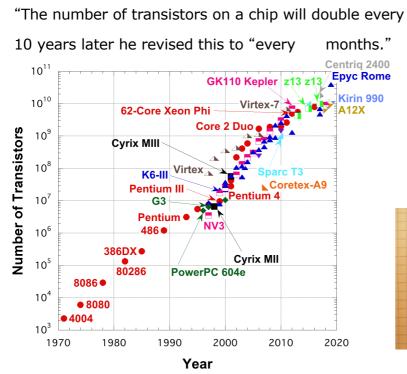

Moore's law : \*

$\rightarrow$  The development speed becomes even faster !

months." (1965)

J

at p.

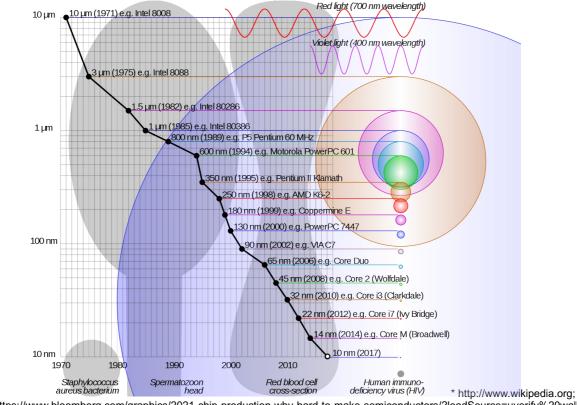

Fabrication rules and technology : \*

https://www.bloomberg.com/graphics/2021-chip-production-why-hard-to-make-semiconductors/?leadSource=uverify%20wall

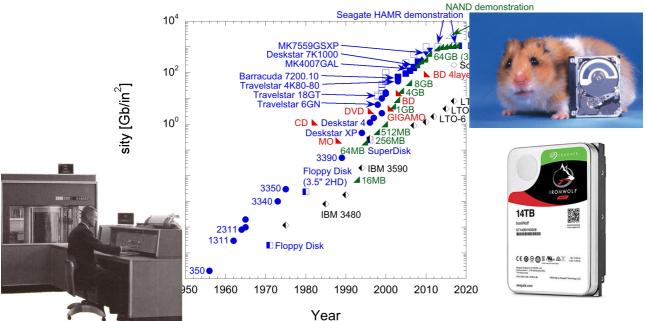

# Increase in Recording Density of Hard Disc Drives

Similar to Moore's law :

Areal density in a hard disc drive (HDD) doubles every months. (~ 1992)

After giant magnetoresistance (GMR) implementation,

it doubles less than every

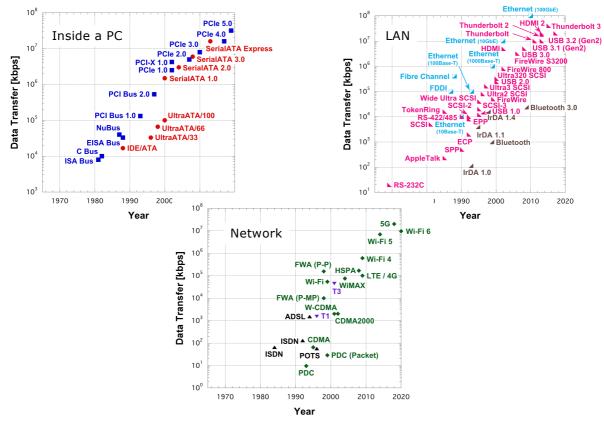

Similar to Moore's law : Data transfer becomes faster.

# Can We Continue Such Trends ?

\* https://www.industryweek.com/emerging-technologies/globalfoundries-gives-advanced-chip-production-technology \*\* https://9to5mac.com/2018/06/21/tsmc-5nm-process-plant/amp/

m-ruled chip : \*

| ×0.64<br>Area ×0.5<br>Density ×2 | 10 |

|----------------------------------|----|

| - Children                       |    |

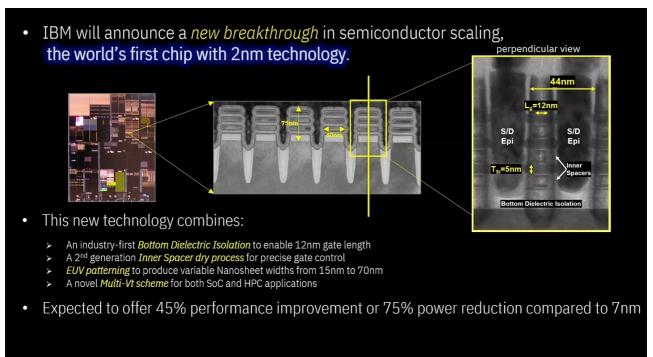

Every decade is the decade that tests the limits of Moore's Law, and this decade is no different. With arrival of Extreme Ultra Volet (EUV) technology, the intricacies of multipatterning techniques develog previous technology nodes can now be applied with the finer resolution that EUV provides. That, alo other more technical improvements, can lead to a decrease in transistor size, enabling the future of semiconductors. To that end, Today IBM is announcing it has created the world's first 2 nanometer n

https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip

|    | Peak Quoted Transistor Densities [MTr/mm <sup>2</sup> ] |        |        |        |         |  |  |  |

|----|---------------------------------------------------------|--------|--------|--------|---------|--|--|--|

|    |                                                         | IBM    | TSMC   | Intel  | Samsung |  |  |  |

|    | 22 nm                                                   |        |        | 16.50  |         |  |  |  |

| 16 | 6 / 14 nm                                               |        | 28.88  | 44.67  | 33.32   |  |  |  |

|    | 10 nm                                                   |        | 52.51  | 100.76 | 51.82   |  |  |  |

|    | 7 nm                                                    |        | 91.20  | 237.18 | 95.08   |  |  |  |

|    | 5 nm                                                    |        | 171.30 |        |         |  |  |  |

|    | 3 nm                                                    |        | 292.21 |        |         |  |  |  |

|    | 2 nm                                                    | 333.33 |        |        |         |  |  |  |

\* https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip

# Latest 2 nm Fabrication Rule

П

In 2021, IBM announced the first demonstration of 2-nm-ruled chip : \*

IBM NDA/Embargo

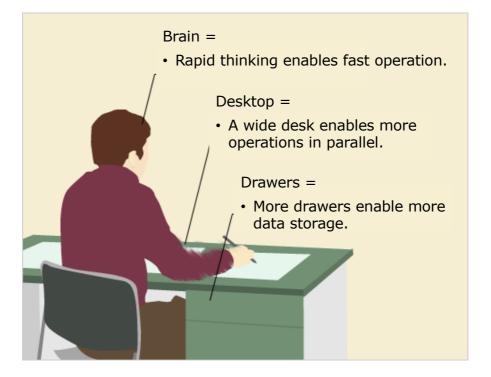

Analogue to our life : \*

\* http://support.nifty.com/tsushin/cs/column/detail/090831543366/1.htm

\* http://www.howstuffworks.com/computer-memory1.htm

X

In 1940s, John von Neumann developed a basic model for a computer.\*

Von Neumann categorised into 5 key components :

- CPU

- Input

- Output

- Working storage

- Permanent storage

\* http://karbosguide.com/books/pcarchitecture/chapter02.htm

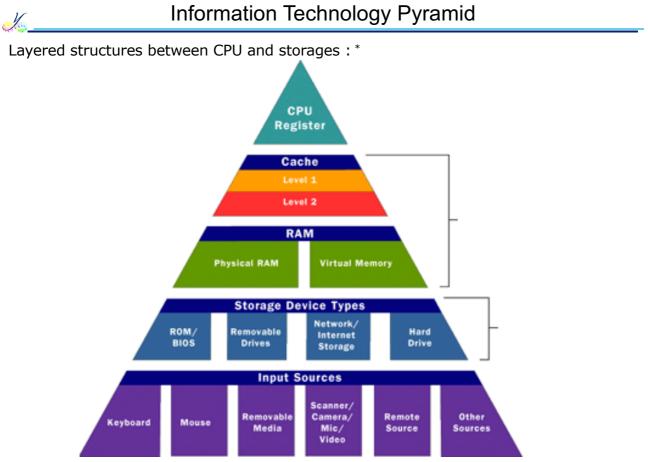

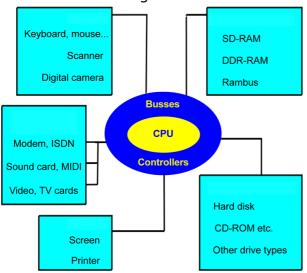

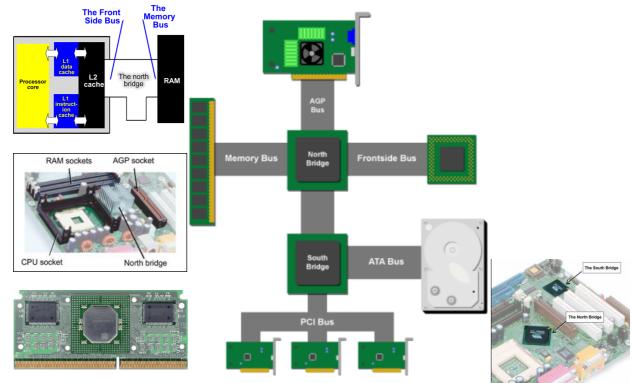

# Connections between the Components

Connections between CPU, in/outputs and storages :

\* http://testbench.in/introduction\_to\_pci\_express.html; \*\* http://karbosguide.com/books/pcarchitecture/chapter06.htm How Does a CPU Work ?

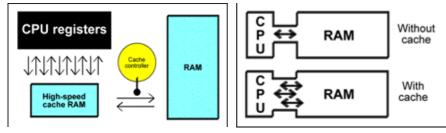

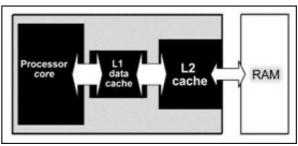

Data transfer between CPU and working storage : \*

A 32-bit CPU can handle data in different sized packets :

• bytes ( bits)

X

- half-words ( bits)

- words ( bits)

- blocks (larger groups of bits)

\* http://karbosguide.com/books/pcarchitecture/chapter10.htm

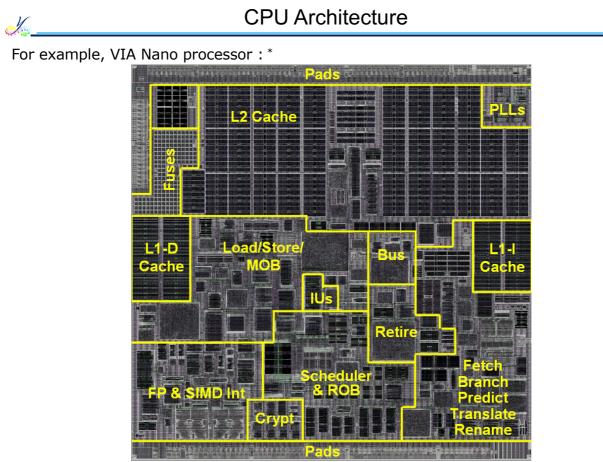

\* http://www.xbitlabs.com/articles/cpu/display/intelatom-vianano\_3.html

#### **CPU** Architecture

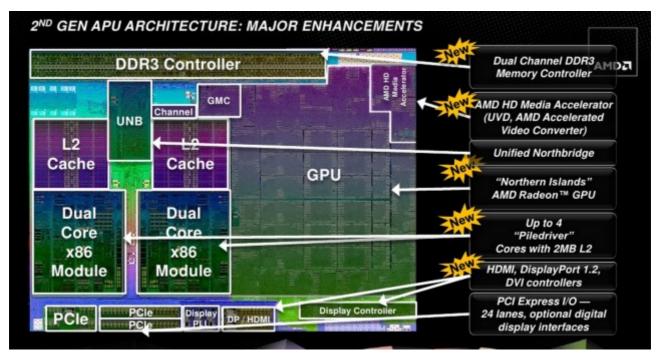

Recent development by AMD, Trinity CPU / GPU architecture :\*

\* https://arstechnica.com/information-technology/2012/05/amd-ships-trinity-processor-aims-for-a-piece-of-intels-ultrabook-market/

Instruction Set Architecture for CPU

Assembly language :

X

CPU can only handle :

• Binary code

Mnemonic :

• ADD / SUB etc.

Number of syntax :

- Typically 100 ~ 200

- Maximum ~ 400

| MONITOR FOR 680                        | 02 1.4                           | 9-14-80 1            | TSC ASSEMBLER PAGE 2                                                       |  |  |  |  |

|----------------------------------------|----------------------------------|----------------------|----------------------------------------------------------------------------|--|--|--|--|

| C000<br>C000 8E 00 70                  |                                  | ROM+\$0000<br>#STACK | ) BEGIN MONITOR                                                            |  |  |  |  |

|                                        |                                  |                      |                                                                            |  |  |  |  |

|                                        |                                  |                      | *****                                                                      |  |  |  |  |

|                                        | * FUNCTION: IN<br>* INPUT: none  |                      | cialize ACIA                                                               |  |  |  |  |

|                                        | * OUTPUT: none                   |                      |                                                                            |  |  |  |  |

|                                        | * CALLS: none                    |                      |                                                                            |  |  |  |  |

|                                        | * DESTROYS: acc A                |                      |                                                                            |  |  |  |  |

| 0013                                   | RESETA EQU                       | 800010011            |                                                                            |  |  |  |  |

| 0011                                   | CTLREG EQU                       | \$00010001           |                                                                            |  |  |  |  |

|                                        |                                  |                      |                                                                            |  |  |  |  |

| C003 86 13                             | INITA LDA A                      | #RESETA              | RESET ACIA                                                                 |  |  |  |  |

|                                        | STA A                            | ACIA<br>#CTUREC      | SET 8 BITS AND 2 STOP                                                      |  |  |  |  |

| C008 86 11<br>C00A B7 80 04            | STA A                            | ACIA                 | SEI 6 BIIS AND 2 SIOP                                                      |  |  |  |  |

|                                        |                                  |                      |                                                                            |  |  |  |  |

| C00D 7E C0 F1                          | JMP                              | SIGNON               | GO TO START OF MONITOR                                                     |  |  |  |  |

|                                        | **********                       | *******              | ******                                                                     |  |  |  |  |

|                                        | * FUNCTION: IN                   | ICH - Input          | character                                                                  |  |  |  |  |

|                                        | * INPUT: none                    |                      |                                                                            |  |  |  |  |

|                                        | * OUTPUT: char<br>* DESTROYS: ac |                      |                                                                            |  |  |  |  |

|                                        | * CALLS: none                    | CC A                 |                                                                            |  |  |  |  |

|                                        |                                  | Gets 1 ch            | maracter from terminal                                                     |  |  |  |  |

| C010 B6 80 04                          | INCH LDA A                       | ACIA                 | GET STATUS                                                                 |  |  |  |  |

| C013 47<br>C014 24 FA                  | ASR A                            |                      | SHIFT RDRF FLAG INTO CARRY<br>RECIEVE NOT READY<br>GET CHAR<br>MASK PARITY |  |  |  |  |

| C014 24 FA                             | BCC                              | INCH                 | RECIEVE NOT READY                                                          |  |  |  |  |

| C016 B6 80 05<br>C019 84 7F            | LDA A                            | ACIA+1               | GET CHAR                                                                   |  |  |  |  |

| C019 84 7F<br>C01B 7E C0 79            | AND A                            | #\$72<br>OUTCH       | GET CHAR<br>MASK PARITY<br>ECHO & RTS                                      |  |  |  |  |

|                                        |                                  |                      |                                                                            |  |  |  |  |

| ************************************** |                                  |                      |                                                                            |  |  |  |  |

|                                        | * INPUT: none                    | HEX - INPU           | JT HEX DIGIT                                                               |  |  |  |  |

|                                        | * OUTPUT: Digi                   | t in acc A           | <b>\</b>                                                                   |  |  |  |  |

| * CALLS: INCH                          |                                  |                      |                                                                            |  |  |  |  |

|                                        | * DESTROYS: ac                   |                      |                                                                            |  |  |  |  |

|                                        | * Returns to m                   | nonitor if           | not HEX input                                                              |  |  |  |  |

| C01E 8D F0                             | INHEX BSR                        | INCH                 | GET A CHAR                                                                 |  |  |  |  |

| C020 81 30                             | CMP A                            | #'0                  | ZERO                                                                       |  |  |  |  |

| C022 2B 11                             |                                  |                      | NOT HEX                                                                    |  |  |  |  |

| C024 81 39<br>C026 2F 0A               | CMP A                            | #'9                  | NINE                                                                       |  |  |  |  |

| C028 81 41                             | CMP A                            |                      | GOOD HEX                                                                   |  |  |  |  |

| C028 81 41                             |                                  | # A<br>HEXERR        | NOT HEX                                                                    |  |  |  |  |

| C02C 81 46                             | CMP A                            | #'F                  |                                                                            |  |  |  |  |

| C02E 2E 05                             |                                  | HEXERR               |                                                                            |  |  |  |  |

| C030 80 07                             |                                  | #7                   | FIX A-F                                                                    |  |  |  |  |

| C032 84 0F<br>C034 39                  | HEXRTS AND A<br>RTS              | #\$0F                | CONVERT ASCII TO DIGIT                                                     |  |  |  |  |

| 0034 33                                | K1S                              |                      |                                                                            |  |  |  |  |

| C035 7E C0 AF                          | HEXERR JMP                       | CTRL                 | RETURN TO CONTROL LOOP                                                     |  |  |  |  |

\* http://www.wikipedia.org/

#### **Memory Access**

Output from one storage based on Address the address. Select one storage based on Selectior the address. Data Write memory Read memory

In principle, only the CPU can (re-)write memory contents : \*

\* A. Nalamori, Interface Feb., 44 (2006).

#### **Read Memory**

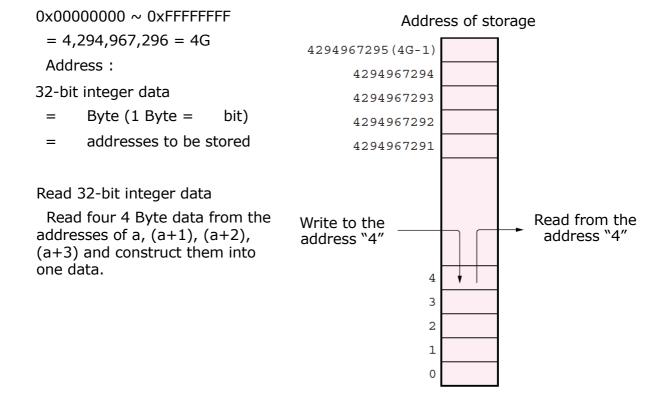

In a 32-bit CPU, the address is typically 32-bit integer : \*

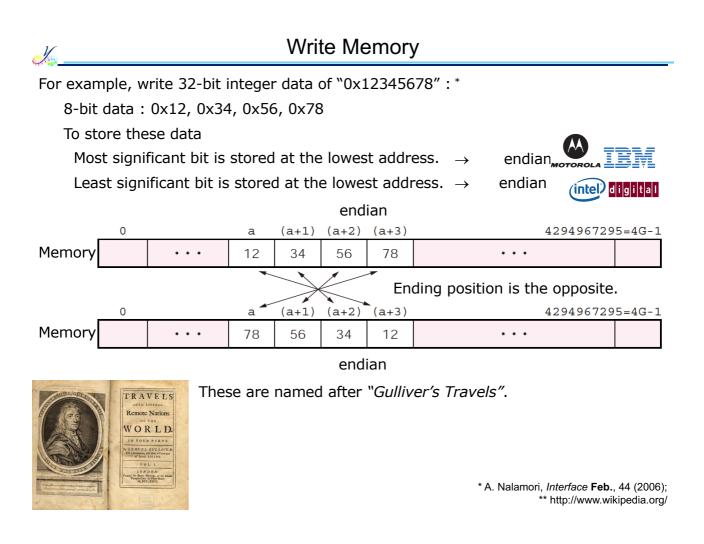

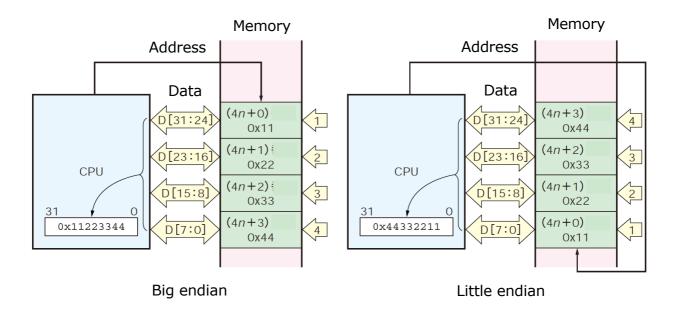

# Memory Access for Big / Little Endian

Data bus holds the same data :

Nowadays most CPU can handle both endianness.

$\rightarrow$  endian

2 = 2 = 3 4 2 = : : : :

#### Byte :

A data unit to represent one letter in Latin character set.

1 byte (B) = bit  $1 \text{ kB} = 1 \text{ B} \times$  $1 \text{ MB} = 1 \text{ kB} \times$ : :