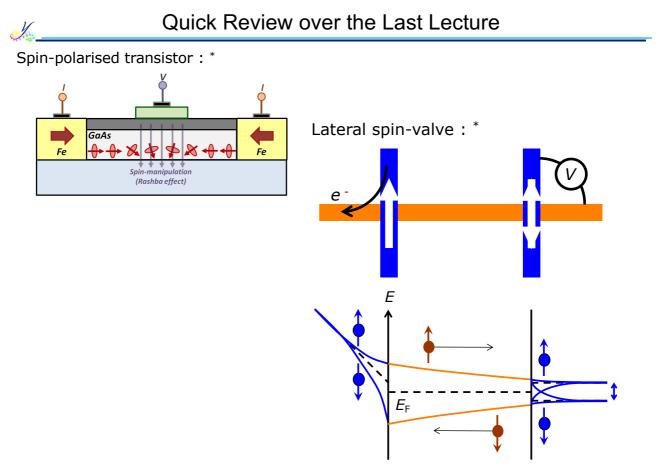

\* S. Datta and S. Das, Appl. Phys. Lett. 56, 665 (1990).

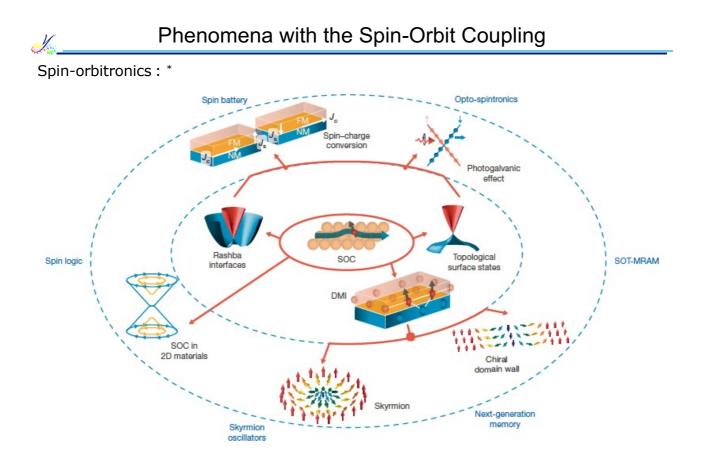

# 17 Spin-Orbit Devices

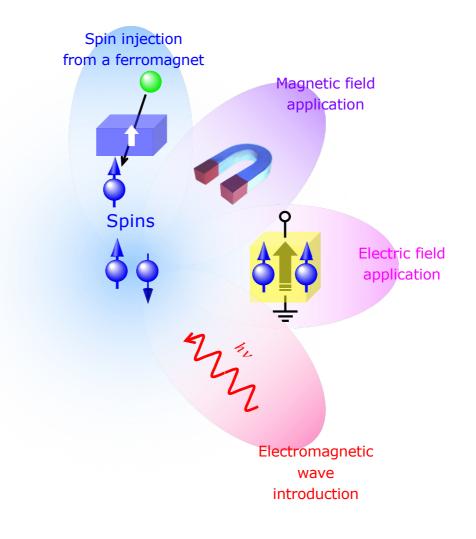

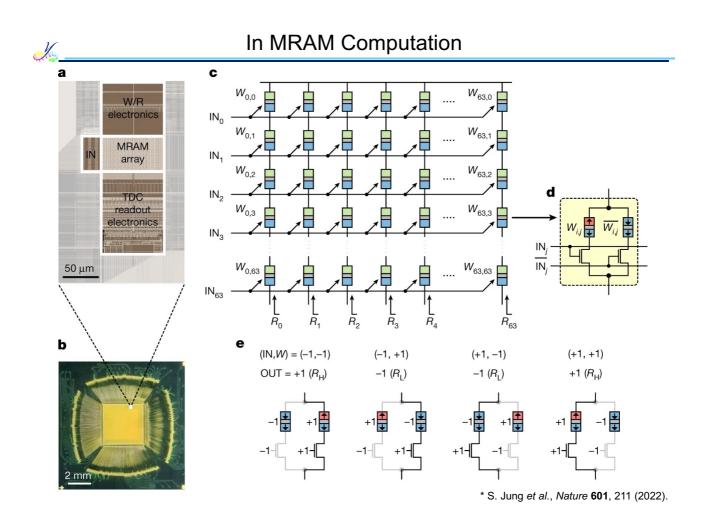

Microwave introduction

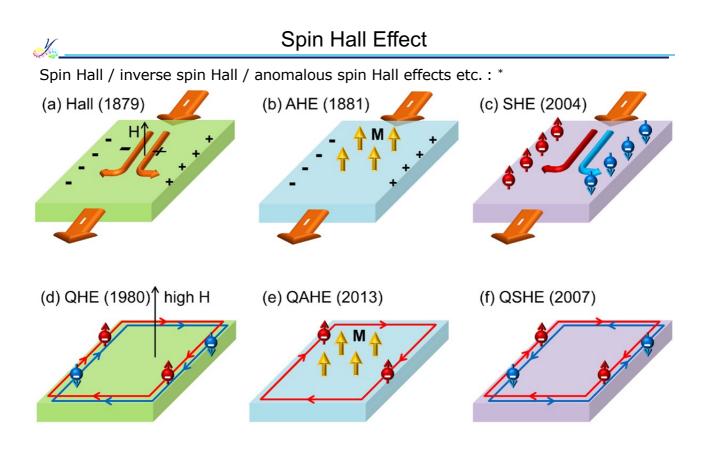

Spin Hall effects

Spin-orbit interactions

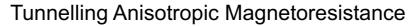

Tunnelling anisotropic magnetoresistance

Topological insulators

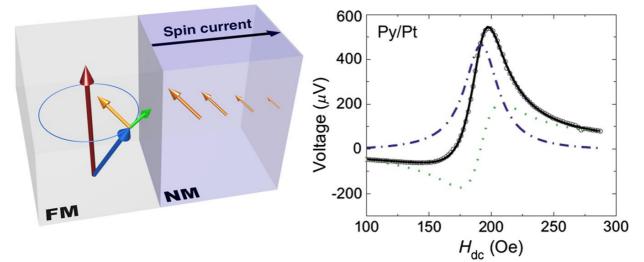

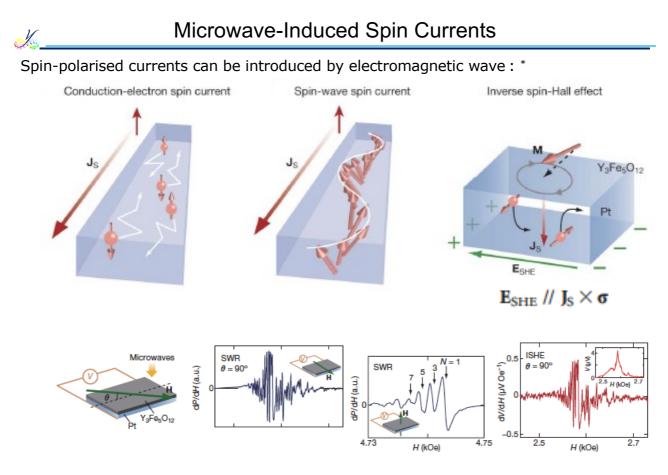

Spin-polarised currents can be introduced by electromagnetic wave : \*

\* O. Mosendz *et al.*, *Phys. Rev. B* **82**, 214403 (2010); A. Hoffmann and S. Bader, *Phys. Rev. Appl.* **4**, 047001 (2015).

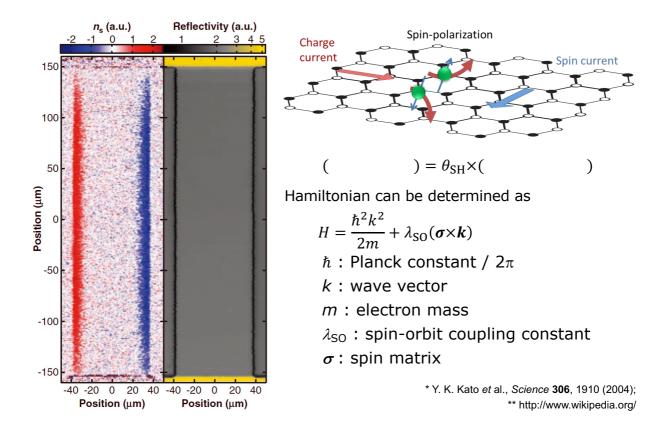

#### Spin Hall Effect in GaAs

MOKE detection of spins generated by the spin Hall effect : \*

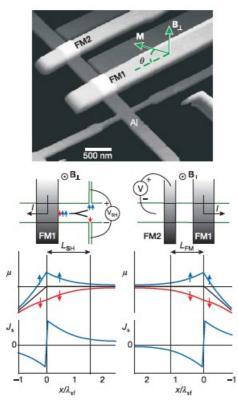

$Co_{0.8}Fe_{0.2}$  /  $AI_2O_3$  / AI nanowires : \*

X

\* S. O. Valenzuela and M. Tinkham, Nature 442, 176 (2006).

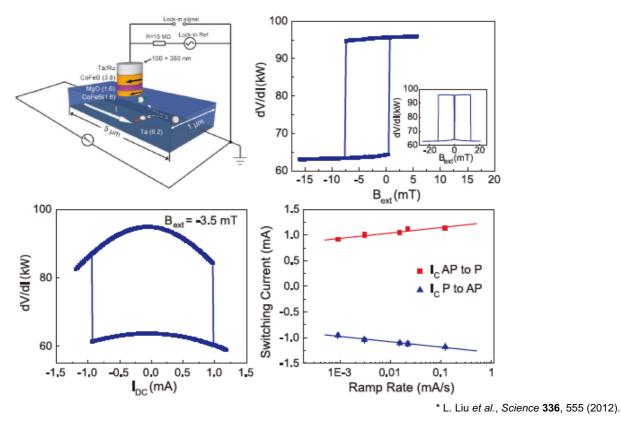

CoFeB / MgO / CoFeB nanopillar on Ta : \*

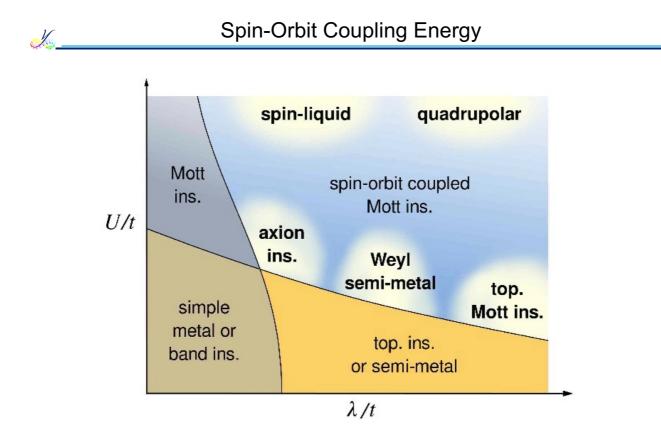

Spin-Orbit Interaction In strongly correlated systems : \* Spin ordering Crystal field splitting Jahn-Teller effect Lattice ordering Bond anisotropy Orbital ordering Crystal field splitting Jahn-Teller effect Lattice ordering Higher cation charg smaller radius smaller coordinates Charge ordering

\* After https://www.slideshare.net/algerien1970/electrical-transport-and-magnetic-interactions-in-3d-and-5d-transition-metal-oxides.

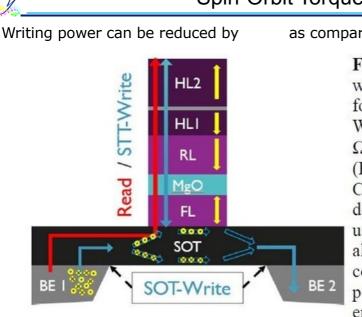

## Spin-Orbit Torque for MRAM

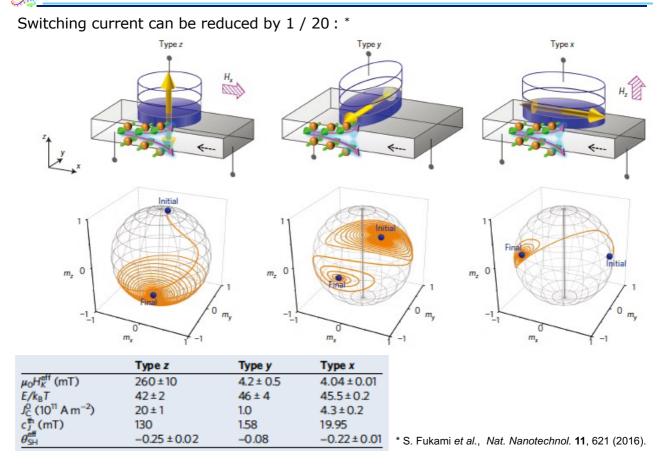

Switching speed can be reduced by 1 / 25 : \*

The switching speed of the SOT-MRAM reached 210 picoseconds while the STT-MRAM, created on the same wafer, clocked a speed of 5 nanoseconds.

\* https://spectrum-ieee-org.cdn.ampproject.org/c/s/spectrum.ieee.org/nanoclast/computing/hardware/sotmram-escapes-from-thelab.amp.html

As a SRAM replacement, MRAM needs faster operation, lower power consumption and longer life :  $^\ast$

| Gen<br>erati<br>on | Туре          | Recording<br>method            | Writing<br>method                                          | Writing<br>speed<br>[ns] | Writing<br>energy<br>[fJ/bit] | Writing<br>life<br>time | Fabrica<br>tion<br>rule<br>[nm] | Recordi<br>ng<br>capacity<br>[Mbit] | Cell<br>configura<br>tion           | Cell<br>size<br>[F <sup>2</sup> ] |

|--------------------|---------------|--------------------------------|------------------------------------------------------------|--------------------------|-------------------------------|-------------------------|---------------------------------|-------------------------------------|-------------------------------------|-----------------------------------|

| 1st                | Field<br>MRAM | In-plane<br>magnetisation      | Magnetic<br>field                                          |                          |                               |                         | 90 ~<br>130                     | < 16                                |                                     |                                   |

| 2nd                | STT-<br>MRAM  | In-plane<br>magnetisation      | Spin-<br>transfer<br>torgue<br>(STT)                       |                          |                               |                         | 40 ~ 65                         | < 256                               |                                     |                                   |

| 3rd                | pSTT-<br>MRAM | Perpendicular magnetisation    | STT                                                        | < 10                     | ~ a few<br>100                | 10 <sup>12</sup>        | 16 ~ 28                         | > 256                               | 2<br>transistor<br>s (T) + 2<br>MTJ | ~ 80                              |

| 4th                | SOT-<br>MRAM  | Perpendicular magnetisation    | Spin-orbit<br>torque                                       |                          | ~ 10                          |                         | 16 ~ 28                         | > 256                               | 2T +<br>1MTJ                        | ~ 40                              |

| 5th?               | VCM           | Perpendicular<br>magnetisation | Voltage-<br>controlled<br>magnetic<br>anisotropy<br>(VCMA) |                          | ~ 3                           |                         | 16 ~ 28                         | > 256                               | 2T + ~<br>10MTJ                     | 4~8                               |

\* https://pc.watch.impress.co.jp/docs/column/semicon/1145577.html

# Spin-Orbit Torque MRAM

as compared with STT : \*

Fig. 1: Schematic of MTJ stack with top-pinned SAF design and following composition: W(SOT) / CoFeB(FL) / MgO (10 $\Omega.\mu m^2) / CoFeB(RL) / SAF$ (HL1-HL2). Compared to STT, SOT writing is

decoupled from TMR reading using 3 terminal geometry, which allows larger cell endurance. SOT converts charge into spin current, perpendicular to the FL, which enables ultra-fast switching.

<u>\_\_\_\_</u>

| O MRAM-info                                                                                                                                                                                                                                                                                              | ο<br>Υοι                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Home About us What is MRAM? STT-MRAM MRAM companies Conferences Spintronics                                                                                                                                                                                                                              | Advertise h                                |

| Home » SOT-MRAM developer Antaios raises \$11 million SOT-MRAM developer Antaios raises \$11 million                                                                                                                                                                                                     | Search th                                  |

| SOT-MRAM developer Antaios raised \$11 million from VCs and Applied Ventures, to accelerate its next-<br>generation memory development and develop new strategic partnerships.                                                                                                                           | f                                          |

|                                                                                                                                                                                                                                                                                                          | 9                                          |

| STT-MRAM bitcell SOT-MRAM bitcell                                                                                                                                                                                                                                                                        | Do<br>Cle                                  |

| SOT-MRAM devices feature switching of the free magnetic layer done by injecting an in-plane current in an<br>adjacent SOT layer, unlike STT-MRAM where the current is injected perpendicularly into the magnetic tunnel<br>junction and the read and write operation is performed through the same path. | <b>Ear</b><br>Q-Grips                      |

| Antaios, established in 2017 in France, is developing SOT-MRAM technology based on research performed at SPINTEC. Other groups around the world are also developing SOT-MRAM technologies, including IMEC, ITRI, NTU and others.                                                                         | Earw:<br>hearin<br>memu<br>this s<br>remov |

| Tags: Investment SOT-MRAM                                                                                                                                                                                                                                                                                |                                            |

| Posted: Sep 17, 2020 by Ron Mertens                                                                                                                                                                                                                                                                      |                                            |

| Log in to post comments                                                                                                                                                                                                                                                                                  |                                            |

### MRAM Roadmap

| SOT Technol      | ogy           |                                    |                                         |          |      |                             |                         |

|------------------|---------------|------------------------------------|-----------------------------------------|----------|------|-----------------------------|-------------------------|

| Field            | 0010          |                                    |                                         |          |      |                             |                         |

|                  | 2012          | 2018                               | 2020                                    | 2022     | 2024 | 2026                        | 2028                    |

| Memory<br>/Logic | SOT switching |                                    | T Field Free<br>• SOT+STT<br>• SOT+CMOS | SOT+VCMA |      | L2, L3 cache<br>Server, HPC | L1 cache,<br>NV-logic   |

| New computing    |               | • SOT N                            | DNN Inference     P-bit ano-contact     | e        | *    | In-memory computing         | Probabilistic computing |

| RF               | • so          | STNO RC T Nano-oscillator     STNC | ) NN                                    |          |      | 🔶 Oscilla                   | tor NN computing        |

L\_\_\_\_

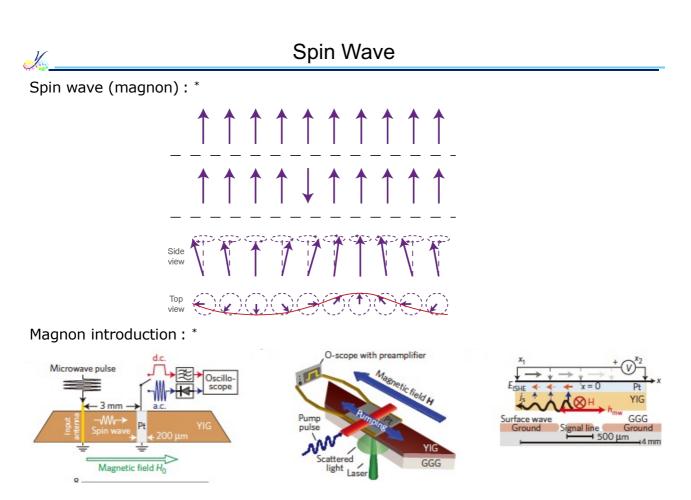

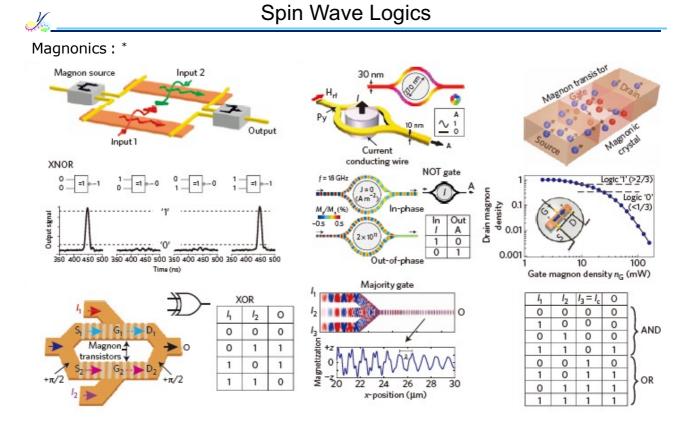

#### Spin Waves

Spin wave (magnon) : \*

The magnon flow can be determined as

$\overrightarrow{J_m} = \hbar \sum_k \overrightarrow{v_k n_k},$

where  $\overrightarrow{v_k}$  is the group velocity of the spin wave  $(=\partial \omega_k / \partial \vec{k})$  and  $n_k$  is the distribution function of the spin wave.

PPHHAR PPPHHAR PP

Analogous

\* A. V. Chumak et al., Nature Phys. 11, 453 (2015).

#### \* Y. Kajiwara et al., Nature 464, 262 (2010).

\* A. V. Chumak et al., Nature Phys. 11, 453 (2015).

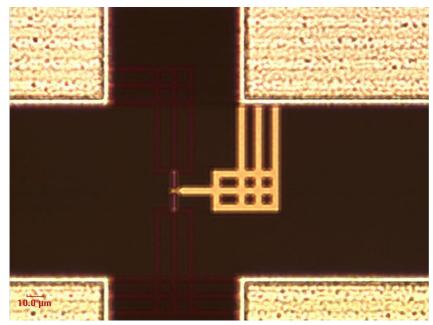

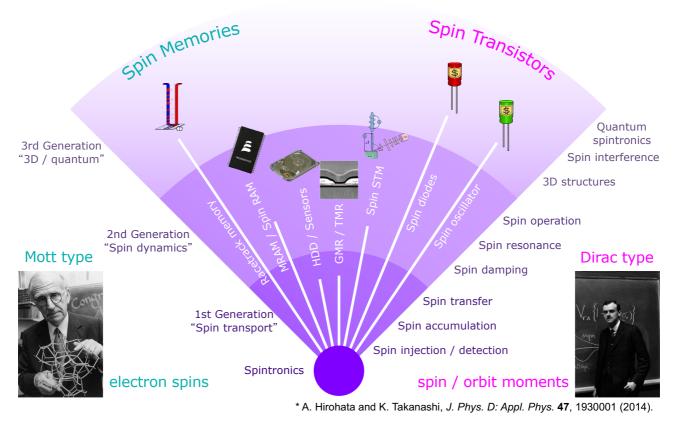

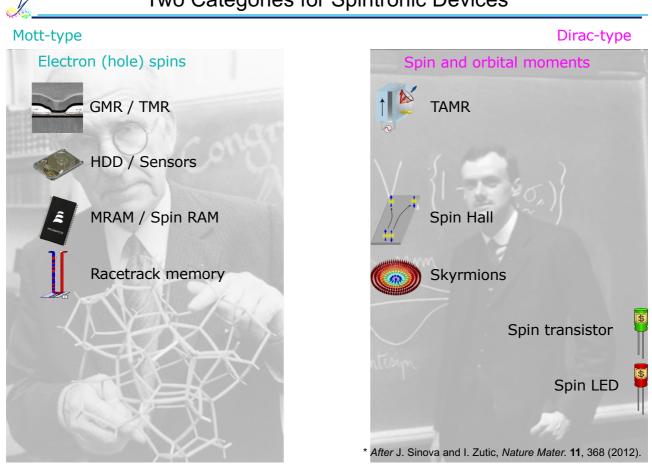

Development of nano-spintronic devices : \*

Two Categories for Spintronic Devices

#### Antiferromagnetic Spintronics

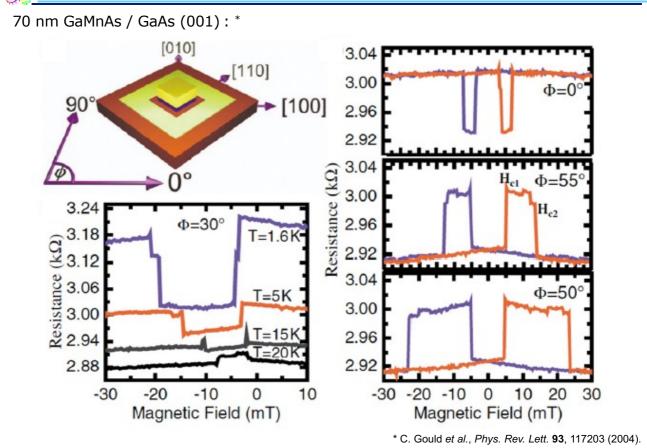

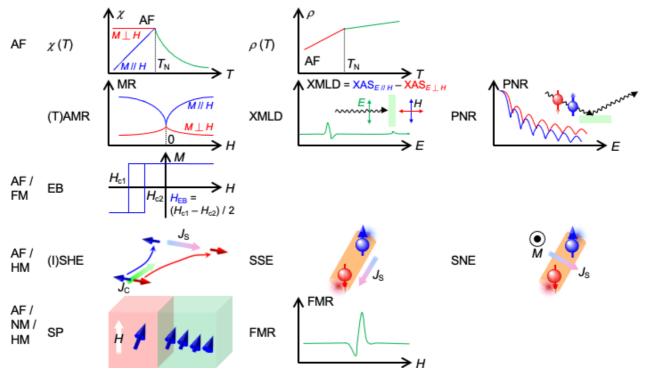

A series of applications have been demonstrated using antiferromagnets : \*

Similar spin-current generation can be achieved with an antiferromagnet : \*

Y

1

\* O. Gomonay *et al.*, *Phys. Status Solidi* **11**, 1700022 (2017); \*\* T. Jungwirth et al., *Nature Nanotechnol.* **11**, 231 (2016).

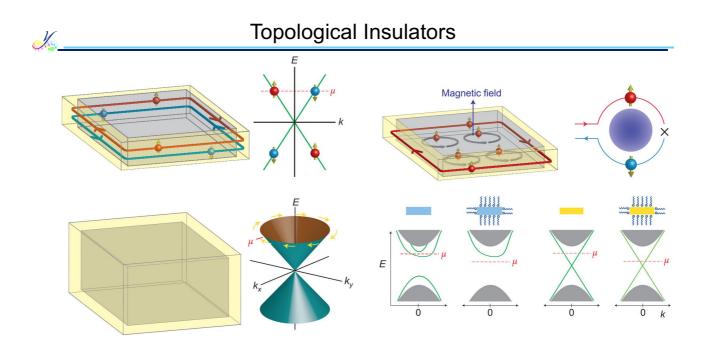

# **Topological Insulators**

\* D. Kong and Y. Cui, Nature Chem. 3, 845 (2011).

#### **Topological Insulators**

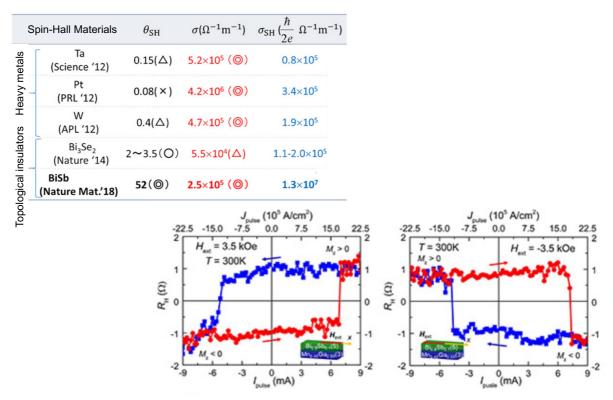

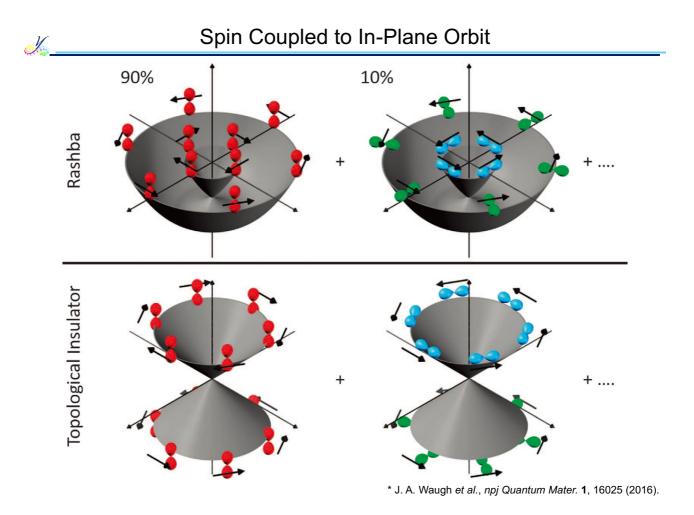

Spin-Hall measurements using topological insulators : \*

X

\* N. H. D. Khang et al., Nat. Mater. 17, 808 (2019).

\* A. Soumyanarayanan et al., Nature 539, 509 (2016).